431-REF-000273

## **Single Event Effect Criticality Analysis**

# Sponsored by NASA HQ/Code QW February 16, 1996

National Aeronautics and Space Administration Goddard Space Flight Center Greenbelt, Maryland

### **TABLE OF CONTENTS**

### <u>Page</u>

| <u>Intro</u> | duction           | •••••        |                                            | Intro-1 |

|--------------|-------------------|--------------|--------------------------------------------|---------|

| <u>1.0</u>   | The S             | SEE Proble   | <u>m</u>                                   | 1-1     |

| <u>2.0</u>   | Func              | tional Anal  | ysis and Criticality                       | 2-1     |

|              | 2.1               | Introduct    | ion                                        |         |

|              | 2.2               |              | al Analysis                                |         |

|              | 2.3               |              | vent Effect Perspective                    |         |

|              | 2.4               | Function     | al Criticality                             | 2-5     |

|              | 2.5               | Function     | al and Device SEE Requirements             | 2-6     |

|              | <u>2.6</u>        | Conclusi     | -<br><u>2n</u>                             | 2-8     |

|              | <u>2.7</u>        | Function     | al Analysis and Criticality References     | 2-8     |

| <u>3.0</u>   | <u>Ioniz</u>      | ing radiatio | n Environment Concerns                     | 3-1     |

|              | <u>3.1</u>        | Ionizing     | Radiation Environment Sources              | 3-1     |

|              |                   | <u>3.1.1</u> | Trapped Heavy Ions and Electrons           |         |

|              |                   | <u>3.1.2</u> | <u>Trapped Protons</u>                     |         |

|              |                   |              | Salactic Cosmic Ray Protons and Heavy Ions |         |

|              |                   |              | olar Flare Protons and Heavy Ions          |         |

|              | <u>3.2</u>        |              | vironments                                 |         |

|              |                   |              | ow Earth Orbits (LEOs)                     |         |

|              |                   |              | Highly Elliptical Orbits (HEOs)            |         |

|              |                   |              | Geostationary Orbits (GEOs)                |         |

|              |                   |              | Planetary and Interplanetary               |         |

|              | <u>3.3</u>        |              | nent Prediction Uncertainties              |         |

|              |                   |              | olar Cycle and Mission Scenarios           |         |

|              |                   |              | <u>rapped Protons</u>                      |         |

|              |                   |              | Galactic Cosmic Ray Heavy Ions             |         |

|              |                   |              | bolar Flare Protons                        |         |

|              | 2.4               |              | <u>bolar Flare Heavy Ions</u>              |         |

|              | $\frac{3.4}{2.5}$ |              | Specific Application                       |         |

|              | <u>3.5</u>        |              | radiation environment concerns References  |         |

| <u>4.0</u>   |                   |              | onic Devices and SEE Rates                 |         |

|              | <u>4.1</u>        |              | vent Upset and Related Effects             |         |

|              |                   |              | Collection of Charge in p-n Junctions      |         |

|              | 1.0               |              | <u>Circuit Effects</u>                     |         |

|              | <u>4.2</u>        |              | ing                                        |         |

|              |                   |              | Sacilities                                 |         |

|              |                   |              | Single-Event Upset Testing                 |         |

|              | 4.2               |              | <u>atchup Testing</u>                      |         |

|              | <u>4.3</u>        | SEE Rate     | <u>e Calculations</u>                      |         |

|            | <u>4.4</u>   | Summary                                                                    | 4-11 |  |

|------------|--------------|----------------------------------------------------------------------------|------|--|

|            | <u>4.5</u>   | Effects in electronic devices and SEE Rates References                     | 4-11 |  |

| <u>5.0</u> | SEU I        | Propagation Analysis: System Level Effects                                 | 5-1  |  |

|            | 5.1          |                                                                            |      |  |

|            | 5.2          | Ground Test and Simulation of System Level or Propagated SEEs              |      |  |

|            | 5.3          | Propagation Analysis Methodology                                           |      |  |

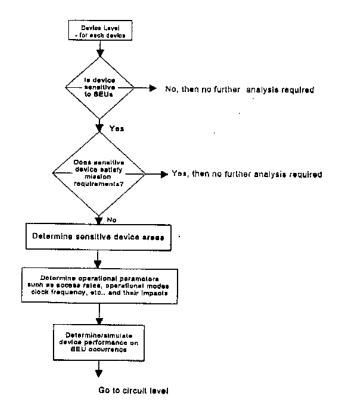

|            |              | 5.3.1 Device Analysis                                                      | 5-3  |  |

|            |              | 5.3.2 <u>Circuit Level Analysis</u>                                        | 5-6  |  |

|            |              | 5.3.3 <u>Higher Level Analysis</u>                                         | 5-7  |  |

|            | <u>5.4</u>   | Example                                                                    | 5-7  |  |

|            | <u>5.5</u>   | Summary                                                                    |      |  |

|            | <u>5.6</u>   | References                                                                 | 5-8  |  |

| <u>6.0</u> | <u>SEE N</u> | Mitigation: Methods of Reducing SEE Impacts                                | 6-1  |  |

|            | <u>6.1</u>   | Introduction                                                               | 6-1  |  |

|            | <u>6.2</u>   | Sample System Level Mitigation Techniques and Examples                     | 6-1  |  |

|            |              | 6.2.1 <u>Classification of System Level SEEs by Device Type</u>            | 6-1  |  |

|            |              | 6.2.2 <u>Mitigation of Memories and Data-Related Devices</u>               | 6-1  |  |

|            |              | 6.2.3 <u>Mitigation of Control-related Devices</u>                         |      |  |

|            |              | 6.2.4 <u>Treatment of Destructive Conditions and Mitigation</u>            |      |  |

|            |              | 6.2.5 <u>Sample Methods of Improving Designs for SEE Performance</u>       |      |  |

|            |              | 6.2.6 Sample Methods of Realistic SEE Risks and Usage                      |      |  |

|            | <u>6.3</u>   | Summary.                                                                   |      |  |

|            | <u>6.4</u>   | Acknowledgements.                                                          |      |  |

|            | <u>6.5</u>   | References for "SEE Mitigation: Methods of Reducing SEE Impacts"           |      |  |

| <u>7.0</u> | <u>Mana</u>  | ging SEEs: System Level Planning                                           | 7-1  |  |

|            | <u>7.1</u>   | Introduction                                                               | 7-1  |  |

|            | <u>7.2</u>   | System Level Requirements for SEE                                          |      |  |

|            | <u>7.3</u>   | Criticality Assignments                                                    |      |  |

|            | <u>7.4</u>   | Allocation of SEE requirements to subsystems                               |      |  |

|            | <u>7.5</u>   | Detailed subsystem SEE design and analysis                                 |      |  |

|            | <u>7.6</u>   | Test and Verification                                                      |      |  |

|            | <u>7.7</u>   | Summary                                                                    |      |  |

| <u>8.0</u> | <u>SEE (</u> | Criticality Assessment Case Studies                                        | 8-1  |  |

|            | <u>8.1</u>   | Design of the AS-1773 Fiber Optic Data Bus for T&C or Payload Applications |      |  |

|            |              | 8.1.1 Background                                                           |      |  |

|            |              | 8.1.2 General Requirements Definition Specific to SEEs                     |      |  |

|            |              | 8.1.3 <u>Environment Description</u>                                       |      |  |

|            |              | 8.1.4 SEE Component Requirements and Design Issues for the AS-1773         |      |  |

|            |              | 8.1.5 SEE Design Verification                                              |      |  |

|            | <u>8.2</u>   | Case Study: Retrofit of a DC to DC Power Converter                         |      |  |

|            | <u>8.3</u>   | SEE Criticality Assessment Case Studies References                         | 8-10 |  |

431-REF-000273

### LIST OF FIGURES

| Figure                                                                                                                                                                                             | Page             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

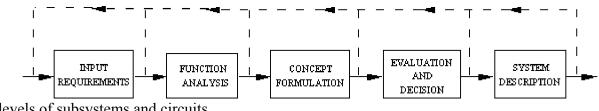

| Figure 2.1 The Systems Engineering Process                                                                                                                                                         | 2-1              |

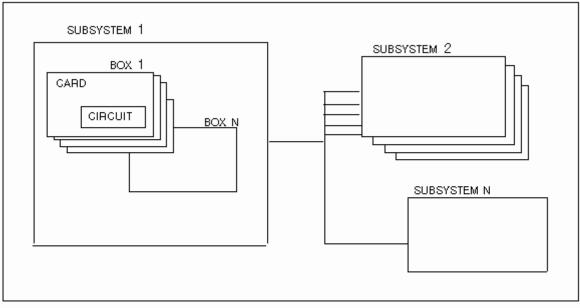

| Figure 2.2 Levels of Physical Design for a Spacecraft                                                                                                                                              | 2-2              |

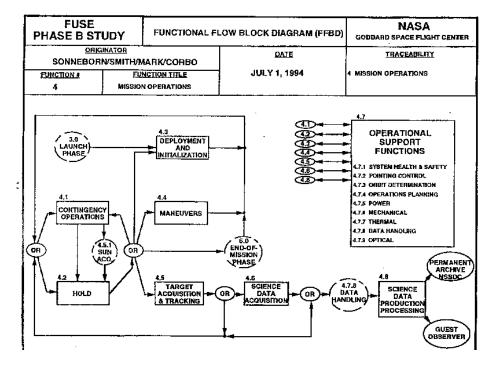

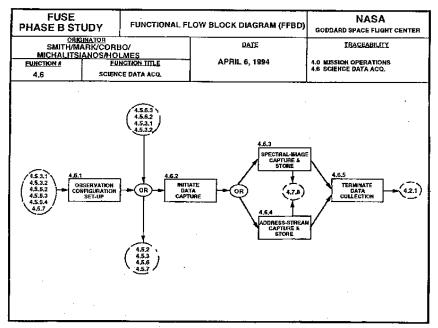

| Figure 2.3 Functional Flow Block Diagram for Mission Operations                                                                                                                                    | 2-3              |

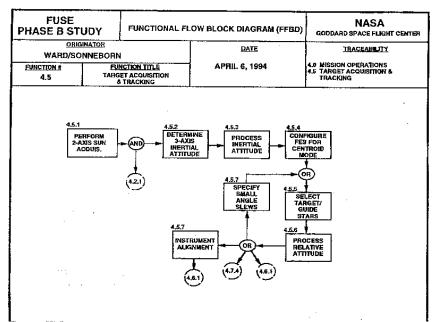

| Figure 2.4 Functional Flow Block Diagram for Target Acquisition & Tracking                                                                                                                         | 2-4              |

| Figure 2.5 Functional Flow Block Diagram for Science Data Acquisition                                                                                                                              | 2-4              |

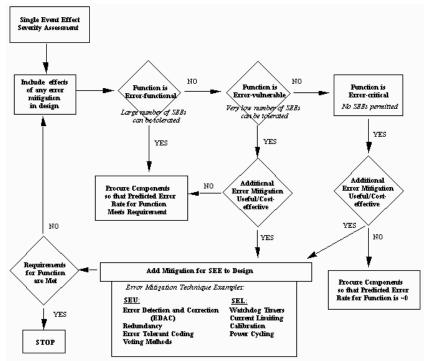

| Figure 2.6 Single Event Effect Decision Tree                                                                                                                                                       | 2-6              |

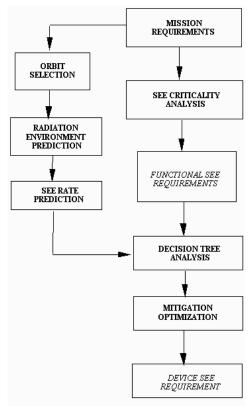

| Figure 2.7 Single Event Effect Requirements Generation                                                                                                                                             | 2-7              |

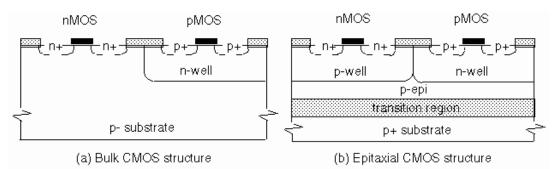

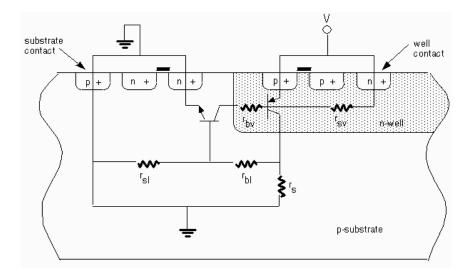

| Figure 4.1 Cross Sections of Bulk and Epitaxial CMOS Processes *Note the difference<br>in the substrate properties.                                                                                | 4-2              |

| Figure 4.2 Latchup paths in a bulk CMOS circuit showing the two parasitic transistors<br>in a four-layer path.                                                                                     | 4-4              |

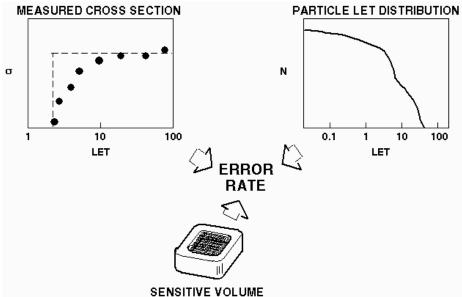

| Figure 4.3 An Illustration of the Three Main Factors that are used in SEE Error Rate Calculat                                                                                                      | <u>ions</u> 4-10 |

| Figure 5.1 Device Level SEU Propagation Methodology                                                                                                                                                | 5-3              |

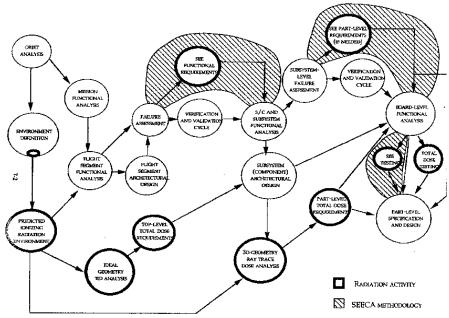

| Figure 7.1 Radiation Analysis Activities in the Systems Definition                                                                                                                                 | 7-1              |

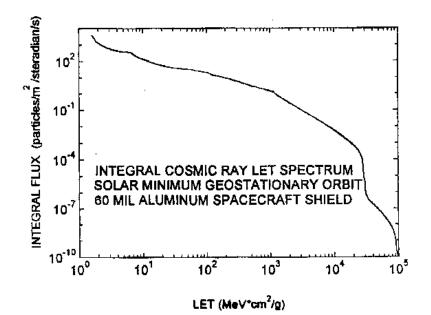

| Figure 8.1 The geostationary cosmic ray environment behind 60 mils Al as calculated for part species and energies during solar minimum.                                                            |                  |

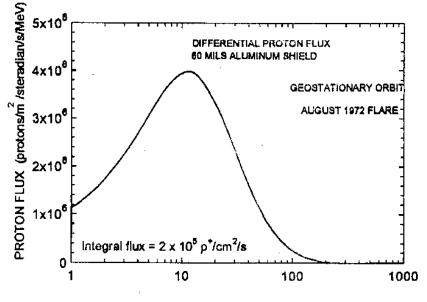

| Figure 8.2 The August 1972 solar flare peak flux environment behind 60 mils Al as<br>calculated using no geomagnetic shielding. The integral flux is calculated for ene<br>penetrating 60 mils Al. |                  |

## LIST OF TABLES

| Table         |                                                          | Page |

|---------------|----------------------------------------------------------|------|

| Table 3.1 Sun | nmary of Radiation Sources                               | 3-6  |

| Table 5.1 San | nple Device Types and Sensitive Areas                    | 5-4  |

| Table 6.1 San | nple EDAC Methods for Memory or Data Devices and Systems | 6-3  |

#### **INTRODUCTION**

Our goal in generating this document is to aid the individuals in project management, systems engineering, radiation effects, and reliability engineering who carry the responsibilities for successful deployment of NASA systems in orbital particle environments. Traditionally, in a manner which may differ from NASA center to NASA center, this effort has involved many iterative passes through system and subsystem designs with involvement of engineers representing the above disciplines. These efforts began in the 1970s when one or two low level integration device types were identified to be susceptible to single event upset (SEU). Since then, with advances in technology, the arena has expanded to include many types of single event effects (SEEs) in many technologies. The necessary advent of SEE hardened device technologies has alleviated some of the worries, but simultaneously added another dimension to the already complex trade space involved in SEE system design and analysis. Indeed, it is the combination of the universal nature of the concern across NASA centers, coupled with the complexities of the issues, which has prompted this study. Our aim is not to prescribe approaches to SEE immune system design, but rather to examine the analysis process and suggest streamlined approaches to the related design problems. In short, we seek to codify the successful elements which, in many cases, already exist for assessing SEE risk and suggest a timeline and procedure for implementing SEE risk analysis with respect to the system design effort.

A combination of factors have converged to impact the growing importance of the traditionally informal single event effects criticality analysis (SEECA). Among these are:

- 1) The increased functionality of satellite systems which impacts the number and complexity of various types of microcircuits,

- 2) The increased device SEE sensitivity commensurate with the smaller feature sizes and advanced technologies (e.g. GaAs signal processors) required to field these systems,

- 3) The difficulty in acquiring space-qualified and SEE tolerant parts and the cost forces driving the use of commercial-off-the-shelf (COTS) parts, and

- 4) The overall complexity of a typical orbital platform which relies on the successful execution of an ever-growing number of instructions.

In short, it is often neither possible nor cost effective to construct systems using SEE immune hardware, and the systems engineer must necessarily make decisions within a trade space including availability, performance, schedule, and cost risk associated with single event effects.

Throughout these discussions we recognize that SEECA covers a highly specialized set of concerns which in many ways parallels conventional reliability analysis. While reliability analysis is by no means simple, the concepts and tools employed by the systems engineering teams and project managers are familiar, and methods exist for both the estimation and quantification of risk. Unfortunately, there seems to be no plausible approach to *direct* application of these tools to single event analyses. This situation is further complicated by the nature of the complex interplay between the environments, mechanisms, effects, and mitigation approaches. This has led to *ad hoc* treatments of single event analyses. On one side, systems engineers have a sometimes incomplete understanding of the exact nature of the risk. On the

other side, experts are familiar with the details of single event effects, particle environments, and radiation hardness issues at the component level but have an incomplete picture of the risk-cost-performance trade space comprising mission reality.

The *ad hoc* approach has evolved as an informal system which works to meet the perceived mission needs, but it can be argued that it is not optimized without the full appreciation by the SEE expert regarding mission requirements and the commensurate understanding of the systems engineers and project managers concerning the SEE risk. The possibility exists to launch with unforeseen and unacceptable risk, or conversely to be overly conservative and lose the battle in terms of the component costs, power requirements, or system complexity through poorly planned actions aimed at controlling these risks. Finally, as with any source of risk, there is potential to overanalyze the problem and thereby expend limited resources through study while overlooking other important risks, SEE rated or otherwise. As mentioned in the NASA Systems Engineering Handbook, this comprises the equivalent of the Heisenberg Uncertainty Principle in risk management.

It is one key aim of this document to pull together the primary elements of single event effects in microelectronics along with the applicable concepts established and proven through years of risk analysis and planning. In the following sections, an overview will be provided for the key elements in the single event risk management "equation". Functional analysis and criticality, which provide the foundation for defining a system and an SEE problem in criticality studies, will be discussed first. A brief discussion on the radiation environment will then be presented. The orbit and time-dependent environment governing the particle types and energies responsible for single event effects will be covered. An overview of the single event interaction mechanisms and the complex matrix of technologies and effects is also provided. Systems-level impacts are determined by analyzing the propagation of SEEs and assessing criticality for which we will also draw on materials to establish approaches from traditional Failure Modes and Effects Analysis (FMEA). Another section will present SEE mitigation techniques, including software mitigation, error tolerance approaches, component-level hardening, and a discussion of the power-speed-cost trades involved. An additional section presents the application of SEECA useful in the generation and flowdown of SEE requirements. A final section will illustrate, by example, application of SEECA in the assessment of SEE-induced failure modes.

Single Event Effect Criticality Analysis offers a methodology to identify the severity of an SEE in mission, system, and subsystem reliability and also provides guidelines for the assessment of SEE-induced failure modes. SEECA may be used in determining the severity of faults caused by SEEs, accounting for criticality of functions performed, and identifying necessity to provide for SEE tolerance. SEECA is intended as a tool for radiation tolerant design, requirements generation for SEEs, design verification, and requirements validation. Ultimately, SEECA will hopefully aid in launching fully functional satellites with acceptable and *understood* SEE risks and with minimum cost, complexity, and power consumption in the final product.

#### 1.0 <u>THE SEE PROBLEM</u>

Radiation damage to on-board electronics may be separated into two categories: total ionizing dose and single event effects. Total ionizing dose (TID) is a cumulative long-term degradation of the device when exposed to ionizing radiation. Single event effects (SEEs) are individual events which occur when a single incident ionizing particle deposits enough energy to cause an effect in a device.

There are many device conditions and failure modes due to SEE, depending on the incident particle and the specific device. It may be convenient to think of two types of SEEs: soft errors and hard errors. Soft errors are nondestructive to the device and may appear as a bit flip in a memory cell or latch, or as transients occurring on the output of an I/O, logic, or other support circuit. Also included are conditions that cause a device to interrupt normal operations and either perform incorrectly or halt. Hard errors may be (but are not necessarily) physically destructive to the device, but are permanent functional effects. Different device effects, hard or soft, may or may not be acceptable for a given design application.

Unlike TID degradation, SEE rates are not evaluated in terms of a time or dose until failure, where the stopwatch begins at launch, but a probability that an SEE will occur within a known span of time. Devices are tested in ground test facilities to characterize the device in a radiation environment. Calculations are also performed to predict the radiation environment for a particular mission orbit. Environment predictions are used with the experimental device data to calculate the probability of occurrence of SEEs in the device for the mission.

Device failure is, of course, of great concern. The effects of propagation of SEEs through a circuit, subsystem, and system are also often of particular importance. The level of impact on the affected circuit, box, subsystem, etc. depends on the type and location of the SEE, as well as on the design. For example, a device error or failure may have effects propagating to critical mission elements, such as a command error affecting thruster firing. There are also cases where SEEs may have little or no observable effect on a system level. In fact, in most designs, there are specific areas which have less system impact from certain radiation effects. The data storage memory in a solid state recorder, for example, may have error detection and correction coding (EDAC) which makes bit errors in the devices transparent to the system. Evaluating the severity of the single event effect hazard involves knowledge from several technical fields including radiation physics, parts engineering, solid state physics, electrical engineering, reliability analysis, and systems engineering.

Both the functional impact of an SEE to the system or spacecraft and the probability of its occurrence provide the foundation for setting a design requirement. System-level SEE requirements may be fulfilled through a variety of mitigation techniques, including hardware, software, and device tolerance requirements. The most cost efficient approach may be an appropriate combination of SEE-hard devices and other mitigation. However, the availability, power, volume, performance, and cost of radiation-hardened devices prohibits their use. Hardware or software design also serve as effective mitigation, but design complexity may present a problem. A combination of the two may be the selected option.

#### Terms and Definitions:

*Single Event Upset* (SEU) is a change of state or transient induced by an ionizing particle such as a cosmic ray or proton in a device. This may occur in digital, analog, and optical components or may have effects in surrounding circuitry. These are "soft" bit errors in that a reset or rewriting of the device causes normal behavior thereafter.

*Single Hard Error* (SHE) is an SEU which causes a permanent change to the operation of a device. An example is a permanent stuck bit in a memory device.

*Single Event Functional Interrupt* (SEFI) is a condition where the device stops normal functions, and usually requires a power reset to resume normal operations. It is a special case of SEU changing an internal control signal.

*Single Event Latchup* (SEL) is a potentially destructive condition involving parasitic circuit elements. In traditional SEL, the device current may exceed device maximum specification and destroy the device if not current limited. A "microlatch" is a subset of SEL where the device current remains below the maximum specified for the device. A removal of power to the device is required in all non-catastrophic SEL conditions in order to recover device operations.

*Single Event Burnout* (SEB) is a highly localized burnout of the drain-source in power MOSFETs. SEB is a destructive condition.

*Single Event Gate Rupture* (SEGR) is the burnout of a gate insulator in a power MOSFET. SEGR is a destructive condition.

*Linear Energy Transfer* (LET) is a measure of the energy transferred to the device per unit length as an ionizing particle travels through a material. The common unit is MeV\*cm<sup>2</sup>/mg of material (Si for MOS devices).

*LET threshold* (LET<sub>th</sub>) is the minimum LET to cause an effect. The JEDEC recommended definition is the first effect when the particle fluence =  $1 \times 10^7$  ions/cm<sup>2</sup>.

*Cross section* (sigma) is the device SEE response to ionizing radiation. For an experimental test for a specific LET, sigma = #errors/ion fluence. The units for cross section are cm<sup>2</sup> per device or per bit.

Asymptotic or saturation cross section (sigma<sub>sat</sub>) is the value that the cross section approaches as LET gets very large.

*Sensitive volume* refers to the device volume affected by SEE-inducing radiation. The geometry of the sensitive volume is not easily known, but some information is gained from test cross section data.

#### 2.0 **FUNCTIONAL ANALYSIS AND CRITICALITY**

#### 2.1 **INTRODUCTION**

Since SEE-inducing particles are, in general, not effectively attenuated with shielding, design tolerance requirements are not based upon location on the vehicle. Instead, SEE requirements depend on the functions devices perform. Many SEEs are different for different device types, e.g. memories will exhibit different conditions than power converters, so the function the device performs is critical to the analysis. In addition, SEEs may present functional impacts by propagating through the design and impacting other areas. These two conditions make each single event problem different in terms of failure mode and effect. SEE analysis is most effectively supported by viewing a design or system from the perspective of the function(s) it performs.

In this section, we present some systems engineering tools useful in constructing and assessing an SEE problem. Functional analysis is an effective method for the consideration of a design for single event effects. The concept of criticality lends itself well to the assessment of the impact of a specific effect. Error propagation analysis, discussed in the following chapter, provides the final link. With the use of these tools, SEECA becomes a specialized Failure Modes and Effects Criticality Analysis (FMECA)-type study.

#### 2.2 **FUNCTIONAL ANALYSIS**

The systems engineering process, presented as one of the Systems Engineering Practices in the MIL-STD-499 Engineering Management Practices, is given in Figure 2.1 [1]. The first box represents the input requirements for the system being considered. With the known performance requirements, one then identifies the required functions to achieve performance, termed "functional analysis". Potential mechanisms to fulfill the functions, or design options, are explored and evaluated. A decision is made, leading to the system description. The process may be applied to many levels in a design, from the large-scale system, or upper-level, to the lower

levels of subsystems and circuits.

**Figure 2.1 The Systems Engineering Process**

Considering a design in terms of function facilitates engineering groups in developing plans and requirements and in performing analyses. Specific to SEECA, it provides the foundation for studying the impact of single event effects (SEEs) on system performance. SEE presents a functional impact on both the device and system levels. By analyzing a design or system in terms of the functions it performs, regardless of its given subsystem name or physical location on the

vehicle, we may form an SEE problem statement and explore solutions. Considering both the device and system in terms of function sets the framework for defining the problem, analyzing it, and exploring solutions.

Different subsystems on a spacecraft are generally associated with different engineering disciplines. The subsystems are typically found on different physical locations on a space vehicle, such as in separate boxes. The attitude control subsystem, for example, is responsible for attaining and maintaining spacecraft orientation. This subsystem usually has several associated boxes which may include earth sensors, sun sensors, reaction wheels, gyros, and support electronics. The command and data handling subsystem may be responsible for issuing, delivering, and storing all computer commands and data. The propulsion subsystem usually contains the on-board thrusters, fuel, and its own electronics. The separation of subsystem boxes is extremely advantageous during design, integration, and test. However, it is easy to overlook the overlapping of functionality. One specific function will often involve hardware and/or software from more than one different subsystem. For example, a reorientation maneuver, when broken down, involves lower level functions in many subsystems: the attitude control system senses orientation data; the command and data handling subsystem generates the required thruster command; and the propulsion subsystem fires a thruster. A schematic of some

SPACEGRAFT

designated levels of design is presented in Figure 2.2.

#### Figure 2.2 Levels of Physical Design for a Spacecraft

Just as the entire systems engineering process in Figure 2.1 applies at many hierarchical levels in design, the functional analysis portion applies similarly. In functional analysis, a design is viewed from the perspective of the functions it performs. The objective of a conventional functional analysis is to define a comprehensive set of baseline functions and functional

performance requirements which must be met in order to accomplish the overall mission objectives. This is achieved through the breakdown of top-level requirements into successively lower-level performance requirements, in a methodical and traceable manner. Functional analysis applied at lower levels involves the breakdown of requirements and functions at the subsystem, card, circuit, and device levels. Top level functional analysis is useful in requirements generation, such as for SEE tolerance. Lower level functional analysis is useful in SEE impact assessment, or failure modes and effects analysis.

Functional analysis may be performed in a clear, methodical way through the use of functional flow block diagrams. This flowchart-like method enables the identification of functions while providing traceability. Figure 2.3 presents a functional flow block diagram created in a mission-level functional analysis effort for the Far Ultraviolet Spectroscopic Explorer mission [2]. Mission operations, specified as function #4, is broken down into the next level, functions 4.1 - 4.7, which include contingency operations, safehold, deployment and initialization, maneuvers, target acquisition & tracking, science data acquisition, and science data processing. Figure 2.4 presents function 4.5, target acquisition & tracking, broken down into its next level, functions 4.5.1 - 4.5.6, which include sun acquisition, inertial attitude determination, inertial attitude processing, sensor configuration, target selection, relative attitude processing, slew specification, and instrument alignment [2]. Science data acquisition, function 4.6, is broken down in Figure

2.5 [2].

Figure 2.3 Functional Flow Block Diagram for Mission Operations

Figure 2.4 Functional Flow Block Diagram for Target Acquisition & Tracking

Figure 2.5 Functional Flow Block Diagram for Science Data Acquisition

For quick studies of design issues, less formal analyses are often useful. Here, many-tiered functional flow block diagrams may not be needed. Quickly drafted notes or even a simple thought experiment may suffice as a short functional analysis on the subsystem or device level.

431-REF-000273

#### 2.3 SINGLE EVENT EFFECT PERSPECTIVE

The systems engineering process is used in many engineering disciplines, including single event effect (SEE) analysis. Some SEE mitigation techniques are system level and are designed directly into the system. For these, system level functional analysis identifies functions that are performed to meet the system requirements. Different system design options mitigating SEE to meet performance requirements may then be considered. Device cost, design complexity, design schedule, system weight and power may be potentially impacted by SEE mitigation, just as with many design selections.

The systems engineering process also applies to device-level SEE analysis. This may be done much later in the design process, after the system baseline has been described. A device has specific requirements associated with it in a design, such as operating current, bit error rate, etc. The device also performs functions to fulfill system level requirements, which may or may not overlap the device requirements. Mitigation schemes at the device level may be considered which ensure that performance requirements are met.

#### 2.4 FUNCTIONAL CRITICALITY

One objective of viewing a design or system in terms of function is to determine the criticality of the function(s) performed on an operational level. Many SEEs present a functional impact, but do not cause permanent damage to the device. Depending on the criticality of a function, these nondestructive conditions may or may not be acceptable in a design. In assessing criticality, we determine the impact of an SEE in a device on the functions it performs. Device hardness requirements are not considered here, since SEEs may be mitigated through many routes. What is of interest is the operational impact of a specific device SEE propagating through the design or system.

Functions may be categorized into "criticality classes", or categories of differing severity of SEE occurrence. Many times, most or all of the functions performed by a design or system are considered critical to a mission. The operational impact of SEEs in critical functions may be unacceptable. For these designs, usually either no single event effects, or a very small probability of SEE occurrences, are permitted. When considering a subsystem, some components may not be SEE-critical, while others may indeed be crucial. For example, the flight data system program memory is certainly critical, while data storage memories may tolerate SEEs if utilizing error correction schemes. Both of these functions are located in the Data System.

In general, one might consider three criticality groups for Single Event Upset: error-functional, error-vulnerable, and error-critical. Functions in the error-functional groups may be unaffected by SEUs, whether it be due to an implemented error-correction scheme or redundancy, and a large probability of SEU may be acceptable. Functions in the error-vulnerable group might be those for which the risk of a low probability is assumable. Functions in the error-critical group are functions where SEU is unacceptable. Figure 2.6 presents a decision tree for criticality analysis, describing a representative criticality grouping and corresponding risk levels, or SEE tolerance requirements [3]. In this discussion, we are applying the decision tree to SEU analysis. One might use Figure 2.6 or a similar process for other nondestructive SEEs.

Figure 2.6 Single Event Effect Decision Tree

This functional criticality concept applies directly at the device level. One may specify the criticality of a device function and determine whether current device tolerance needs and mitigation schemes are adequate to protect the system from impacts. Functional criticality is also a direct lead into SEE requirements generation on any level, including spacecraft, system, and subsystem.

#### 2.5 FUNCTIONAL AND DEVICE SEE REQUIREMENTS

Once the criticality of functions are determined, requirements for design, including hardware and software may be directly obtained. In the criticality analysis presented in Figure 2.6, the requirements for SEU probability for all three criticality groups are directly tied to acceptable risks. The more critical an SEE is to operational performance, the more strict the SEE requirement should be.

In general, the tradeoff in the development of SEE requirements is risk vs. cost and design complexity. The more risk assumed, the higher the allowable probability of an SEE, and potentially the less the cost of the design. There may be cases in which a greater percentage of SEEs may be acceptable for a reduction in cost. Other design concerns also play a role, such as performance, power, weight, and volume.

Requirements are specified for each functional group by specifying the maximum probability of SEE occurrence permitted in each category. The SEE rate requirements may be different for SEU, latchup, gate rupture, and any other SEE of concern. These requirements are specified at

the functional level, and are achievable through many avenues, including hardware mitigation, software schemes, redundancy, and device hardness. In contrast to specifying a spacecraft-level requirement, *functional SEE requirements* may yield areas in the design, or specific functions, with lower necessary tolerance levels. This reduction in requirements usually translates to a reduction in the cost of design. However, common devices across functions might be cost-advantageous under the worst-case radiation specification. The decision tree in Figure 2.6 is again helpful here. For each criticality group, there is a functional requirement. The functional requirement may be fulfilled using a combination of methods. The selection of mitigation tools leads to the device requirement. A functional requirement does not necessarily translate directly to a device requirement. Figure 2.7 presents this requirements flow [3].

Figure 2.7 Single Event Effect Requirements Generation

This idea of functional and device SEE requirements is useful when working at many levels in design. Some projects perform a complete spacecraft functional analysis as part of the systems engineering responsibility. In this case, functional SEE requirements for the entire design, or any portion of it, may be directly derived by categorizing the functional breakdown by criticality. For specific portions of a design, functional SEE requirements may be developed by detailing the functions performed in that portion. Device SEE requirements flow directly from both of these, as described earlier. If addressing a problem in more detailed design phase, device SEE requirements may be determined by assessing the functional criticality of specific components and assessing mitigation options to meet the specified operational requirements.

#### 2.6 CONCLUSION

This section has presented some discussion on functional analysis and criticality, two systems engineering tools for design assessment. It is hoped that these methods will facilitate SEE analysis, both in forming a problem statement and arriving at solutions. Depending on the application, this methodology may be used in its entirety or in various degrees.

#### 2.7 FUNCTIONAL ANALYSIS AND CRITICALITY REFERENCES

- 1. MIL-STD-499A, "Engineering Management," May 1974.

- 2. Smith, Terrence, private communication, NASA Goddard Space Flight Center, May 5, 1994.

- 3. Gates, Michele and LaBel, Kenneth, "A Systems Engineering Approach to the Design of Survivable Electronics for the Natural Space Ionizing Radiation Environment," AIAA paper 95-0843, Jan. 1995.

- 4. LaBel, K. and Gates, M., "Single Event Effect Mitigation from a System Perspective," IEEE Transactions on Nuclear Science Special Edition, 1996.

#### 3.0 IONIZING RADIATION ENVIRONMENT CONCERNS

The definition of the radiation environment for SEE predictions must provide sufficient information to meet two criteria:

- 1) What is the "normal" radiation environment under which the system must operate? In other words, will the mitigation measures and mission operation plans be adequate to handle the SEU rates during normal operation times?

- 2) What is the "worst case" radiation environment that the mission will encounter? In other words, will the levels of radiation during a pass through the peak fluxes of the proton belts or at the peak of a solar flare result in catastrophic data loss or cause parts to experience permanent or semi-permanent damage?

This section is intended to inform SEECA users of the risks, unknowns, and uncertainties inherent in radiation environment predictions. Thus, they will be better able to define SEE mitigation requirements that reduce risk with reasonable cost.

#### 3.1 IONIZING RADIATION ENVIRONMENT SOURCES

The main sources of energetic particles that are of concern to spacecraft designers are:

- 1) Protons and electrons trapped in the Van Allen belts,

- 2) Heavy ions trapped in the magnetosphere,

- 3) Cosmic ray protons and heavy ions, and

- 4) Protons and heavy ions from solar flares.

The levels of all of these sources are affected by the activity of the sun. The solar cycle is divided into two activity phases: the solar minimum and the solar maximum. An average cycle lasts about eleven years with the length varying from nine to thirteen years [1, 2, 3]. Generally, the models of the radiation environment reflect the particle level changes with respect to the changes in solar activity.

#### 3.1.1 Trapped Heavy Ions and Electrons

From the information provided by the mapping of the trapped heavy ions by the SAMPEX satellite [4], we know that these ions do not have sufficient energy to penetrate the satellite and to generate the ionization in electronic parts necessary to cause SEEs. Also, electrons are not known to induce SEEs. Therefore, trapped heavy ions and trapped electrons are not included in a radiation environment definition for SEEs and will not be discussed in the sections below.

#### 3.1.2 Trapped Protons

In the past, analyses of SEEs focused on energetic heavy ion induced phenomena. However, SEE data from recent spacecraft [5, 6, 7] have shown that newer, high density electronic parts can

have higher upset rates from protons than from heavy ions because of their low threshold LET value. In addition, it is difficult to shield against the high energy protons that cause SEE problems within the weight budget of a spacecraft. As a result, any successful and cost effective SEE mitigation plan must include a careful definition of the trapped proton environment and its variations.

Protons are the most important component of the "inner" Van Allen belt. In the equatorial plane, the high energy protons (E>30 MeV) extend only to about 2.4 earth radii. The energies range from keV to hundreds of MeV. The intensities range from 1 proton/cm<sup>2</sup>/sec to 1 x  $10^5$  protons/cm<sup>2</sup>/sec. The location of the peak flux intensities varies with particle energy. This is a fairly stable population but three known variations are important when defining requirements for SEE analyses. The most well known variation in the population is due to the cyclic activity of the sun. During solar maximum, the trapped proton populations near the atmospheric cut-off at the inner edge of the belt are at the lowest levels and, during solar minimum, they are at their highest. Second, the trapped protons are subject to perturbations at the outer edge of the inner belt and in the region between two and three earth radii due to geomagnetic storms and/or solar flare events. Last, the particle population is affected by the gradual change (secular variation) of the earth's magnetic field.

Trapped proton levels are calculated using the NASA AP8 model [8]. In the model, flux intensities are ordered according to field magnitude (B) and dipole shell parameter (L). The AP8 model comes in solar minimum and solar maximum versions, therefore, it is possible to take into account the solar cycle variations by simply selecting the appropriate model version. Otherwise, the models are static and do not reflect the variations due to storms and the geomagnetic field changes. Consequently, the trapped proton fluxes from the AP8 model represent omnidirectional, integral intensities that one would expect to accumulate on an average over a six month period of time. For limited durations, short term excursions for the models averages can reach orders of magnitude above or below.

Analyses of data gathered in flight before, during, and after geomagnetic storms and solar flare events have shown that the trapped proton population is affected by these phenomena at the outer edges of their trapping domain. It was observed on the CRRES satellite that flew during solar maximum that the so called "slot" region of the magnetosphere (2 < L < 3) can become filled with very energetic trapped protons as a result of solar flare events. The decay time of the second belt is estimated to be on the order of 6-8 months. Phillips Laboratory has modeled this second proton belt as detected by the CRRES satellite [10]. The Air Force DMSP satellite flew during solar minimum. Particle flux monitors on board the DMSP showed that, after a major magnetic storm, the inner proton belt was reconfigured and eroded such that a second belt was formed [11]. A model of this redistribution of particles is not available.

To address the problem of the variation in the particle population due to the changes in the geomagnetic field, it has become a common practice to obtain fluxes from the AP8 model by using geomagnetic coordinates (B,L) calculated for the epoch of AP8 model (1964 for solar minimum and 1970 for solar maximum). This practice came about with the observation that, by using the actual epoch of the mission (e.g., 1995) for the geomagnetic coordinates for orbits at

low altitudes (<1000 km), unrealistically high levels of fluxes are obtained from the models due to a lack of an atmospheric cutoff condition in the AP8 [12]. However, B,L coordinates calculated with 1964 and 1970 epochs must be used with caution because it has been shown by in-flight proton flux measurements at an altitude of 541 kilometers [13] that the predictions obtained with geomagnetic coefficients for 1970 can result in significant errors in the spatial placement of the particle populations. This error is usually averaged out when the proton fluence is orbit integrated over a period of 24 hours or greater but it can result in errors when specific positions in space are analyzed.

#### 3.1.3 Galactic Cosmic Ray Protons and Heavy Ions

Galactic cosmic ray particles originate outside the solar system. They include ions of all elements from atomic number 1 through 92. The flux levels of these particles are low but, because they include highly energetic particles (10s of MeV/n ~ E ~ 100s of GeV/n) of heavy elements such as iron, they produce intense ionization as they pass through matter. As with the high energy trapped protons, they are difficult to shield against. Therefore, in spite of their low levels, they constitute a significant hazard to electronics in terms of SEEs.

As with the trapped proton population, the galactic cosmic ray particle population varies with the solar cycle. It is at its peak level during solar minimum and at its lowest level during solar maximum. The earth's magnetic field provides spacecraft with varying degrees of protection from the cosmic rays depending primarily on the inclination and secondarily on the altitude of the trajectory. However, cosmic rays have free access over the polar regions where field lines are open to interplanetary space. The exposure of a given orbit is determined by rigidity functions calculated with geomagnetic field models [14]. The coefficients in the models include a time variation so that the rigidity functions can be calculated for the epoch of a mission.

The levels of galactic cosmic ray particles also vary with the ionization state of the particle. Particles that have not passed through large amounts of interstellar matter are not fully stripped of their electrons. Therefore, when they reach the earth's magnetosphere, they are more penetrating than the ions that are fully ionized. The capacity of a particle to ionize material is measured in terms of LET and is primarily dependent on the density of the target material and to a lesser degree the density and thickness of the shielding material.

Several models of the cosmic ray environment are available including CRÈME [15], CHIME [16], and a model by Badhwar and O'Neill [17]. The model most commonly used at this time is CREME; however, CHIME is based on more recent data from the CRRES satellite. The authors of CREME recommend that most of the environment options available in CREME not be used because they are outdated or inaccurate [18]. They suggest that the standard solar minimum calculations be used for most applications (M=1) and that a worst case estimate should be obtained using the singly ionized model (M=4). Reference 16 compares the CHIME and CREME models and includes a brief discussion of the Badhwar and O'Neill model.

The CREME and CHIME models include solar cycle variations and magnetospheric attenuation calculations. The CREME model calculates LET for a simple shield geometry for aluminum shields and targets. CHIME improves the LET calculations by permitting the user to choose a

shield material density and a target material density. Also, the CHIME model assumes that the anomalous component of the environment is singly ionized.

#### 3.1.4 Solar Flare Protons and Heavy Ions

As mentioned in Section 3.1, work by Feynman et al. [2, 3] and Stassinopoulos et al. [1] shows that an average eleven year solar cycle can be divided into four inactive years with a small number of flare events (solar minimum) and seven active years with a large number of events (solar maximum). During the solar minimum phase, few significant solar flare events occur; therefore, only the seven active years of the solar cycle are usually considered for spacecraft mission evaluations. Large solar flare events may occur several times during each solar maximum phase. For example, in cycle 21 there were no events as large as the August 1972 event of cycle 20; whereas, there were at least eight such events in cycle 22 for proton energies greater than 30 MeV. The events last from several hours to a few days. The proton energies may reach a few hundred MeV and the heavy ion component ranges in energy from 10s of MeV/n to 100s of GeV/n. As with the galactic cosmic ray particles, the solar flare particles are attenuated by the earth's magnetosphere. The rigidity functions that are used to attenuate those particles can also be used to attenuate the solar flare protons and heavy ions. When setting part requirements, it is important to keep in mind that solar flare conditions exist for only about two percent of the total mission time during solar maximum.

An empirical model of the solar flare proton environment based on solar cycle 20 has existed since 1973 [19]. In 1974 King introduced a probabilistic model of the solar cycle 20 events [20]. This model divides events into "ordinary" and "anomalously large" (AL) and predicts the number of AL events for a given confidence level and mission duration. Stassinopoulos published the SOLPRO model [21] based on King's analysis. Since data for more solar cycles have become available, Feynman et al. [2,3] have concluded that the proton fluence distributions actually form a continuum of events between "ordinary" the "anomalously large" flares. A team at JPL has combined the results of several works into the JPL Solar Energetic Particle Event Environment Model (JPL92) [22]. This model consists of three parts: a statistically based model of the proton fluence, and a heavy ion composition model.

The solar flare proton portion of the JPL92 model predicts essentially the same fluences as the SOLPRO code for the solar flare proton energies that are important for SEE analysis (E>30 MeV). However, for worst case analyses, the peak solar flare proton flux is required and neither model contains this information. The peak flux of the protons for the August 1972 event can be obtained from the CREME model by specifying M=9 and element number = 1.

For the 26 events observed on the CRRES satellite [16], the peak fluxes for the helium ions with energies E > 40 MeV/n were three times higher than the galactic cosmic ray heavy ion levels. Above the energy of a few hundred MeV/n, the solar flare levels merge with those of the galactic cosmic ray background. The CREME model of the solar flares assumes that the solar particle events with the highest proton fluxes are always heavy ion rich. However, Reames et al. [23] contradict this assumption in their study of the ISEE 3 data. They found an inverse correlation

between proton intensity and the iron/carbon heavy ion abundance ratio and that the composition of the flare was a result of the location of the flare on the sun.

The JPL92 model includes a definition of the solar flare heavy ion component based on the data from the IMP series of satellites. A paper by McKerracher et al. [24] gives an excellent overview of that model and presents sample calculations for interplanetary space at 1 AU. One of the findings of this work is that the JPL92 model calculates more realistic and lower solar heavy ion induced SEE rates. The CHIME model also contains a definition of the solar flare heavy ion fluence. As with the JPL92 model, it is expected that the CHIME model will predict lower SEE rates due to solar heavy ions.

### **3.2 ORBIT ENVIRONMENTS**

There are extremely large variations in the SEE inducing flux levels that a given spacecraft encounters depending on its trajectory through the radiation sources. Some of the typical orbit configurations are discussed below with emphasis given to considerations that are important when calculating SEE rate predictions.

#### 3.2.1 Low Earth Orbits (LEOs)

The most important characteristic of the environment encountered by satellites in LEOs is that several times each day they pass through the proton and electron particles trapped in the Van Allen belts. The level of fluxes seen during these passes varies greatly with orbit inclination and altitude. The greatest inclination dependencies occur in the range of  $0^{\circ} < i < 30^{\circ}$ . For inclinations over  $30^{\circ}$ , the fluxes rise more gradually until about  $60^{\circ}$ . Over  $60^{\circ}$  the inclination has little effect on the flux levels. The largest altitude variations occur between 200 to 600 km where large increases in flux levels are seen as the altitude rises. For altitudes over 600 km, the flux increase with increasing altitude is more gradual. The location of the peak fluxes depends on the energy of the particle. For trapped protons with E > 10 MeV, the peak is at about 4000 km. For normal geomagnetic and solar activity conditions, these proton flux levels for energies E > 10 MeV have been detected at these higher altitudes after large geomagnetic storms and solar flare events.

The amount of protection that the geomagnetic field provides a satellite from the cosmic ray and solar flare particles is also dependent on the inclination and to a smaller degree the altitude of the orbit. As altitude increases, the exposure to cosmic ray and solar flare particles gradually increases. However, the effect that the inclination has on the exposure to these particles is much more important. As the inclination increases, the satellite spends more and more of its time in regions accessible to these particles. As the inclination reaches polar regions, it is outside the closed geomagnetic field lines and is fully exposed to cosmic ray and solar flare particles for a significant portion of the orbit.

Under normal magnetic conditions, satellites with inclinations below 45° will be completely shielded from solar flare protons. During large solar events, the pressure on the magnetosphere will cause the magnetic field lines to be compressed resulting in solar flare and cosmic ray

particles reaching previously unattainable altitudes and inclinations. The same can be true for cosmic ray particles during large magnetic storms.

#### 3.2.2 Highly Elliptical Orbits (HEOs)

Highly elliptical orbits are similar to LEO orbits in that they pass through the Van Allen belts each day. However, because of their high apogee altitude (greater than about 30,000 km), they also have long exposures to the cosmic ray and solar flare environments regardless of their inclination. The levels of trapped proton fluxes that HEOs encounter depend on the perigee position of the orbit including altitude, latitude, and longitude. If this position drifts during the course of the mission, the degree of drift must be taken into account when predicting proton flux levels.

#### 3.2.3 Geostationary Orbits (GEOs)

At geostationary altitudes, the only trapped protons that are present are below energy levels necessary to initiate the nuclear events in materials surrounding the sensitive region of the device that cause SEEs. However, GEOs are almost fully exposed to the galactic cosmic ray and solar flare particles. Protons below about 40-50 MeV are normally geomagnetically attenuated, however, this attenuation breaks down during solar flare events and geomagnetic storms. Field lines that cross the equator at about 7 earth radii during normal conditions can be compressed down to about 4 earth radii during these events. As a result, particles that were previously deflected have access to much lower latitudes and altitudes.

#### 3.2.4 Planetary and Interplanetary

The evaluation of the radiation environment for these missions can be extremely complex depending on the number of times the trajectory passes through the earth's radiation belts, how close the spacecraft passes to the sun, and how well known the radiation environment of the planet is. Each of these factors must be taken very carefully into account for the exact mission trajectory.

Careful analysis is especially important for missions that fly during solar maximum and that have trajectories that place the spacecraft close to the sun. Guidelines for scaling the intensities of particles of solar origin for spacecraft outside of 1 AU have been determined by a panel of experts [25]. They recommend that a factor of 1 AU x  $1/r^2$  be used for distances less than 1 AU and that values of 1 AU x  $1/r^3$  be used for distances greater than 1 AU.

| Radiation<br>Source | Models              | Effects of Solar<br>Cycle                   | Variations                                                | Types of Orbits<br>Affected  |

|---------------------|---------------------|---------------------------------------------|-----------------------------------------------------------|------------------------------|

| Trapped<br>Protons  | AP8-MIN;<br>AP8-MAX | Solar Min -<br>Higher; Solar<br>Max - Lower | Geomagnetic Field; Solar<br>Flares; Geomagnetic<br>Storms | LEO; HEO;<br>Transfer Orbits |

| Galactic            | CREME;              | Solar Min -                                 | Ionization Level                                          | LEO; GEO; HEO;               |

#### Table 3.1 Summary of Radiation Sources

| Radiation<br>Source       | Models                         | Effects of Solar<br>Cycle                                     | Variations                                                                           | Types of Orbits<br>Affected                 |

|---------------------------|--------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------|

| Cosmic Ray<br>Ions        | CHIME;<br>Badhwar &<br>O'Neill | Higher; Solar<br>Max - Lower                                  |                                                                                      | Interplanetary                              |

| Solar Flare<br>Protons    | SOLPRO;<br>JPL92               | Large Numbers<br>During Solar<br>Max; Few During<br>Solar Min | Distance from Sun<br>Outside 1 AU; Orbit<br>Attenuation; Location of<br>Flare on Sun | LEO (I>45°);<br>GEO; HEO;<br>Interplanetary |

| Solar Flare<br>Heavy Ions | CREME;<br>JPL92; CHIME         | Large Numbers<br>During Solar<br>Max; Few During<br>Solar Min | Distance from Sun<br>Outside 1 AU; Orbit<br>Attenuation; Location of<br>Flare on Sun | LEO; GEO; HEO;<br>Interplanetary            |

#### 3.3 ENVIRONMENT PREDICTION UNCERTAINTIES

Actual flight data have shown that SEE rates are clearly influenced by the dynamics of the radiation environment. The section above mentions some of the uncertainties inherent in predicting the radiation environment for a mission. The purpose of this section is to specifically address the factors that must be considered to reduce uncertainties.

Experience has shown that the most effective means of reducing uncertainty factors and design margins in particle predictions is to define for the mission:

- 1. When the mission will fly,

- 2. Where the mission will fly

- 3. Mission duration,

- 4. When the systems will be deployed,

- 5. What systems must operate during worst case environment conditions,

- 6. What systems are critical to mission success, and

- 7. The amount of shielding surrounding the SEE sensitive part(s).

We caution against using old predictions from previous missions. As discussed in the sections above, the predictions have large variations that are a function of altitude, inclination, model used, and time of the mission.

#### 3.3.1 Solar Cycle and Mission Scenarios

Particle level predictions based on the actual mission scenarios are lower than those based on taking the worst case prediction for every environment. Estimates that include only worst case conditions lead to over-design and should be used only in the concept design phase of a mission when the actual launch date and length have not been defined. After the launch date and duration are defined, it is possible to estimate how long the spacecraft will be in each phase of the solar cycle. These estimates should consider the impact of a launch delay of one year. Mission scenario definition is especially important for solar flare particles where the number of events is highly dependent on the amount of time that the satellite spends in solar maximum conditions.

#### 3.3.2 Trapped Protons

The uncertainty factor defined for the trapped proton AP8 model is two. This is based on the statistical error inherent in merging the several spacecraft data sets that make up the model and does not include the substantial variations that occur over time. The largest variability in the trapped proton predictions is a function of the trajectory of the spacecraft. Therefore, applying proton predictions for a satellite in one orbit trajectory to another trajectory can result in errors up to several orders of magnitude.

To reduce the uncertainty of trapped proton calculations for SEE application, the definition of the trapped proton environment must specifically take into account:

- 1. How long the mission will be in each phase of the solar cycle and the effect of changes in the launch date,

- 2. The orbit trajectory,

- 3. Analysis of the effects of the secular variation of the geomagnetic field (especially for orbits under 1000 km),

- 4. Analysis of the variation in the outer edges of the proton trapping regions due to solar flare events/magnetic storms, and

- 5. The amount of spacecraft shielding surrounding the SEE sensitive part(s).

#### 3.3.3 Galactic Cosmic Ray Heavy Ions

The basic uncertainty factor defined for the CREME model is two. The CHIME model will provide more updated abundances when it is available.

To reduce the uncertainty in the predictions of the galactic cosmic ray heavy ion levels, the definition must consider:

- 1. How long the mission will be in each phase of the solar cycle and the effect of changes in the launch date,

- 2. The effect of the ionization state of the anomalous component,

- 3. The amount of geomagnetic shielding for the orbit, and

- 4. Estimate of the amount of shielding surrounding the SEE sensitive part(s).

#### 3.3.4 Solar Flare Protons

The component of the environment that presents the largest uncertainty in predictions is the solar flare protons. Some solar cycles (Cycle 21) contain no extremely large flares at all. Other cycles contain as many as eight extremely large events (Cycle 22). The problem of providing solar flare predictions to those concerned with SEE criticality analysis is compounded by the limitations of the models. They are designed for determining mission integrated total dose or solar cell degradation levels and do not adequately address the SEE problem. That is, they provide event integrated fluences (SOLPRO) or mission integrated and daily fluences (JPL92). These values are not adequate for determining worst case SEE vulnerability during the peak flux levels of the flares. The new CHIME model promises to provide these options for users when it becomes available. In the meantime, the best option is to use the peak flux spectrum from the August 1972 event [14]. The fluence levels provided by the SOLPRO and JPL92 models are a function of confidence level and mission duration.

To reduce the uncertainty in solar flare proton predictions, the definition must take into account:

- 1. How long the mission will be in each phase of the solar cycle and the effect of changes in the launch date,

- 2. The level of confidence selected by the project,

- 3. Fluence levels for an extremely large event,

- 4. Flux levels for the peak of an event,

- 5. The amount of geomagnetic shielding for the orbit,

- 6. Estimate of how many times such an event will occur, and

- 7. The amount of shielding surrounding the SEE sensitive part(s).

#### 3.3.5 Solar Flare Heavy Ions

The JPL92 model provides a significant improvement over the CREME model for the solar flare heavy ion compositions. As with the solar flare proton portion of the model, the heavy ion model gives fluences as a function of confidence level and mission duration. Again, for SEE analysis, a peak spectrum must be analyzed for worst case conditions.

The solar flare heavy ion predictions must take into account:

- 1. How long the mission will be in each phase of the solar cycle and the effect of changes in the launch date,

- 2. The level of confidence selected by the project,

- 3. Fluence levels for an extremely large event,

- 4. Flux levels for the peak of an event,

- 5. The amount of geomagnetic shielding for the orbit,

- 6. Estimate of how many times such an event will occur, and

- 7. The amount of shielding surrounding the SEE sensitive part(s).

#### 3.4 MISSION SPECIFIC APPLICATION

It is not as easy to define the radiation environment for SEE requirements as for TID requirements. In specifying a TID environment, all components of the environment (electrons, protons, bremsstrahlung) are converted to dose units (rads) and summed. The SEE-inducing environment may consist of both protons and heavy ions. Since the underlying physics of the interactions of protons and heavy ions are different, the SEE prediction models and the environment input required are not the same. In general, heavy ions cause upsets via direct ionization of the sensitive regions in the device. The LET spectrum for the particular orbit is used to define this portion of the SEE-inducing radiation environment. Proton-induced upsets are usually caused by secondaries produced by nuclear collisions in the material surrounding the sensitive node of the device. The energy of the incident proton is the best predictor of the damage potential as it determines the levels of secondary heavy ions produced by the collisions. Therefore, the proton energy spectrum is used to define this component of the SEE-inducing radiation environment. In rare cases, where the LET threshold of the device is very low (< 1 MeV\*cm<sup>2</sup>/mg), the protons can directly ionize the sensitive regions. One example is the 1773 fiber optic data bus. In these situations, the LET spectrum of the protons is used, rather than the proton energy spectrum.

SEE predictions are further complicated by the large variation in the criticality levels of system components. For example, it is not necessary to apply worst case solar flare proton conditions that occur for only a few days of the mission to a data recording system that is not required to maintain data integrity during the flares. These are "normal operation" conditions, hence, environments to consider are daily averages, worst case passes through the South Atlantic Anomaly (SAA), and background cosmic ray heavy ions. On the other hand, devices that control critical functions must be able to operate at all times and may have the requirement that no SEEs are permitted. If this is the case, worst case environments are defined and applied, such as, peak fluxes in the SAA and peak solar flare conditions.

It is most advantageous to a mission if the radiation environment specialist is involved as soon as mission requirements are set. In fact, there are cases where it benefits the mission to have advice on radiation environment levels during the orbit selection process. Experience has shown that it is possible to reduce radiation exposure by choosing more benign regions of space while still meeting mission goals. In the SEE requirements generation flow (Figure 2.7), the radiation environment prediction and subsequent SEE predictions for the parts on the preliminary parts list occurs in parallel with setting system functional requirements. At this phase in the mission, a nominal shielding value must be set (e.g., 60 mils). The environment predictions and SEE predictions will be for this shielding value in the requirements generation at the point where decision tree analysis begins.

After setting functional requirements and predicting SEE rates, device sensitivity and criticality are taken into account if further mitigation is necessary. (See Figure 2.6, Single Event Decision Tree). In the case of devices with a low threshold LET (implying probable sensitivity to protons), it may be beneficial to evaluate the actual shielding geometry to determine if a lower, more accurate SEE prediction can be defined. The obvious advantage of this "mitigation" approach is the potential cost savings in eliminating or reducing design impacts. In the case of heavy ions, shielding is not likely to have an effect on the rate of SEE occurrence.

After mission planners have determined the mission specifications, they should provide the radiation environment specialists with:

- 1. The orbit configuration,

- 2. The date of launch,

- 3. The mission duration, and

- 4. The nominal shielding thickness(es).

The definition of the radiation environment for SEE analyses based on the above parameters should include (if applicable for the orbit):

- 1. Trapped proton spectra attenuated by the nominal shielding thickness(es) for:

- a. Orbit averaged daily fluences,

- b. Fluences for worst case pass through the SAA, and

- c. Peak fluxes in the SAA;

- 2. LET spectrum for the nominal shield thickness(es) for orbit attenuated, galactic cosmic ray heavy ions;

- 3. Orbit attenuated solar flare proton spectra attenuated by the nominal shielding thickness(es) for:

- a. An entire solar flare event and

- b. The peak of an event;

- 4. LET spectrum for the nominal shield thickness(es) for orbit attenuated, solar heavy ions for:

- a. An entire solar flare event and

- b. At the peak of an event.

If any devices are susceptible to direct ionization by protons, it is necessary to include the LET spectrum for trapped and solar flare protons for the nominal shielding thickness(es) in the definition of the radiation environment.

#### 3.5 IONIZING RADIATION ENVIRONMENT CONCERNS REFERENCES

- 1. E.G. Stassinopoulos, G.J. Brucker, D.W. Nakamura, C.A. Stauffer, G.B. Gee, J.L. Barth, "Solar Flare Proton Evaluation at Geostationary Orbits for Engineering Applications," accepted for publication in IEEE Special Transactions of Nuclear Science, April 1996.

- 2. J. Feynman, T.P. Armstrong, L. Dao-Gibner, and S. Silverman, "New Interplanetary Proton Fluence Model," J. Spacecraft, Vol. 27, No. 4, pp. 403-410, Jul.-Aug. 1990.

- 3. J. Feynman and S. Gabriel, "A New Model for Calculation and Prediction of Solar Flare Proton Fluences," AIAA 90-0292, 28th Aerospace Sciences Meeting, Reno, Nevada, Jan.8-11, 1990.

- 4. J.R. Cummings, A.C. Cummings, R.A. Mewaldt, R.S. Selesnick, E.C. Stone, T.T. von Rosenvinge, and J.B. Blake, "SAMPEX Measurements of Heavy Ions Trapped in the Magnetosphere," IEEE Trans. on Nuc. Sci., Vol. 40, No. 6, pp. 1458-1462.

- K.A. LaBel, S. Way, E.G. Stassinopoulos, C.M. Crabtree, J. Hengemihle, and M.M. Gates, "Solid-state Tape Recorders: Spaceflight SEU Data for SAMPEX and TOMS/Meteor-3," IEEE Radiation Effects Data Workshop Record, pp. 77-84, 1993.

- 6. A. Campbell, P. McDonald, and K. Ray, "Single Event Upset Rates in Space," IEEE Trans. on Nuc. Sci., Vol. 39, No. 6, pp. 1829-1835, December 1992.

- J. Adolphsen, J.L. Barth, E.G. Stassinopoulos, T. Gruner, M. Wennersten, K.A. LaBel, C.M. Seidleck, "Single Event Upset Rates on 1 Mbit and 256 Kbit Memories: CRUX Experiment on APEX," IEEE Trans. on Nuc. Sci., Vol. 42, No. 6, pp. 1964-1974, December 1995.

- 8. D.M. Sawyer and J.I. Vette, "AP-8 Trapped Proton Environment for Solar Maximum and Solar Minimum," NSSDC/WDC-A-R&S, 76-06, December 1976.

- E.G. Mullen, M. S. Gussenhoven, K. Ray, and M. Violet, "A Double-peaked Inner Radiation Belt: Cause and Effect as Seen on CRRES," IEEE Trans. on Nuc. Sci., Vol. 38, No. 6, pp. 1713-1717, December 1991.

- M.S. Gussenhoven, E.G. Mullen, M.D. Violet, C. Hein, J. Bass, and D. Madden, "CRRES High Energy Proton Flux Maps," IEEE Trans. on Nuc. Sci., Vol 40, No. 6, pp. 1450-1457, December 1993.

- 11. M.S. Gussenhoven, E.G. Mullen, and E. Holman, "Radiation Belt Dynamics During Solar Minimum," IEEE Trans. on Nuc, Sci., Vol. 36, No. 6, pp. 2008-2014, December 1989.

- 12. P.D. McCormick, "Radiation Dose and Shielding for the Space Station," Acta Astronautica, 17, p. 231, 1988.

- C.S. Dyer, A.J. Sims, P.R. Truscott, J. Farren, and C. Underwood, "Radiation Environments on Shuttle Missions Using the CREAM Experiment," IEEE Trans. on Nuc. Sci., Vol. 39, No. 6, pp. 1809-1816, December 1992.

- 14. IAGA Working Group, "International Geomagnetic Reference Field, 1991 Revision", EOS Transactions of AGU, Vol. 73, No. 16, April 21, 1992.

- 15. J.H. Adams, Jr., "Cosmic Ray Effects on Microelectronics, Part IV," NRL Memorandum Report 5901, December 31, 1987.

- 16. D.L. Chennete, J. Chen, E. Clayton, T.G. Guzik, J.P. Wefel, M. Garcia-Munoz, C. Lapote, K.P. Ray, E.G. Mullen, and D.A. Hardy, "The CRRES/SPACERAD Heavy Ion Model of the Environment (CHIME) for Cosmic Rays and Solar Particle Effects on Electronic and Biological Systems in Space," Trans. on Nuc. Sci., Vol. 41, No. 6, pp. 2332-2339, December 1994.

- 17. G.D. Badhwar and P.M. O'Neill, "An Improved Model of the Galactic Cosmic Radiation for Space Exploration Missions," Nucl. Tracks Radiat. Meas., 20, No. 3, pp. 403-410, 1992.

- E.L. Petersen, J.C. Pickel, J. H. Adams, Jr., and E.C. Smith, "Rate Prediction for Single Event Effects - A Critique," IEEE Trans. on Nuc. Sci., Vol. 39, No. 6, pp. 1577-1599, December 1992.

- 19. E.G. Stassinopoulos and J.H. King, "Empirical Solar Proton Model for Orbiting Spacecraft Applications," IEEE Trans. on Aerospace and Electronic Systems, Vol. AES-10, No. 4, pp. 442-450, July 1974.

- 20. J.H. King, "Solar Flare Proton Fluences for 1977-1983 Space Missions," J. Spacecraft and Rockets," 11: pp. 401-408, 1974.

- E. G. Stassinopoulos, "SOLPRO: A Computer Code to Calculate Probabilistic Energetic Solar Flare Fluences," NSSDC 75-11, National Space Science Data Center, Greenbelt, Maryland, April 1975.

- 22. G. Murphey, D. Croley, M. Cherng, and G. Spitale, "The JPL Solar Energetic Particle Event Environment Model," presentation material from September 1992.

- 23. D. V. Reames, H. V. Cane, and T. T. von Rosenvinge, "Energetic Particle Abundances in Solar Electron Events," The Astrophys. J., 357, pp. 259-270, July 1, 1990.

- 24. P. L. McKerracher, J. D. Kinnison, and R. H. Maurer, "Applying New Solar Flare Particle Event Models to Interplanetary Satellite Programs," IEEE Trans. on Nuc. Sci., Vol. 41, No. 6, pp. 2368-2375, December 1994.

- 25. M.A.Shea et al., "Toward a Descriptive Model of Solar Particles in the Heliosphere", Workshop on Interplanetary Charged Particle Environment, JPL, March 1987.

#### 4.0 <u>EFFECTS IN ELECTRONIC DEVICES AND SEE RATES</u>

#### 4.1 SINGLE-EVENT UPSET AND RELATED EFFECTS

#### 4.1.1 <u>Collection of Charge in p-n Junctions</u>